Voici la troisième et dernière partie de mon compte-rendu d’une visite au cœur de l’une des usines les plus modernes de France : les unités de production de Crolles et Grenoble de STMicroelectronics, effectuée le 3 décembre 2014.

La première partie décrivait la filière française des semiconducteurs et les activités de STMicroelectronics. La seconde portait sur la Fab300 de Crolles et les procédés de fabrication des chipsets. Ici, nous passons en revue deux unités de production : le packaging et le test, situées à Grenoble.

Grenoble – unité de packaging

L’unité de packaging de Grenoble que j’ai pu visiter n’est pas une unité de production de volume. Elle est dédiée au développement des procédés d’assemblage et à l’assemblage des derniers prototypes des circuit qui sortent des fabs de Crolles. Elle fonctionne donc à petite échelle par rapport aux unités de back-end situées en Asie, à Malte ou au Maroc.

J’ai pu y prendre des photos. On y rentrait en se couvrant d’une combinaison, comme pour la Fab300 de Crolles, la salle étant aussi sous atmosphère contrôlée.

Les étapes de packaging sont assez nombreuses :

- On commence par polir la face arrière des wafers silicium dans trois machines utilisant des grains différents. L’objectif est d’adapter l’épaisseur du wafer au boitier utilisé. Le wafer peut perdre au passage jusqu’aux quatre cinquièmes de son épaisseur. C’est particulièrement utile pour les circuits destinés à des appareils mobiles et avec des cartes mères miniaturisées à l’extrême.

- Les wafers sont ensuite découpés avec des machines de découpe automatique.

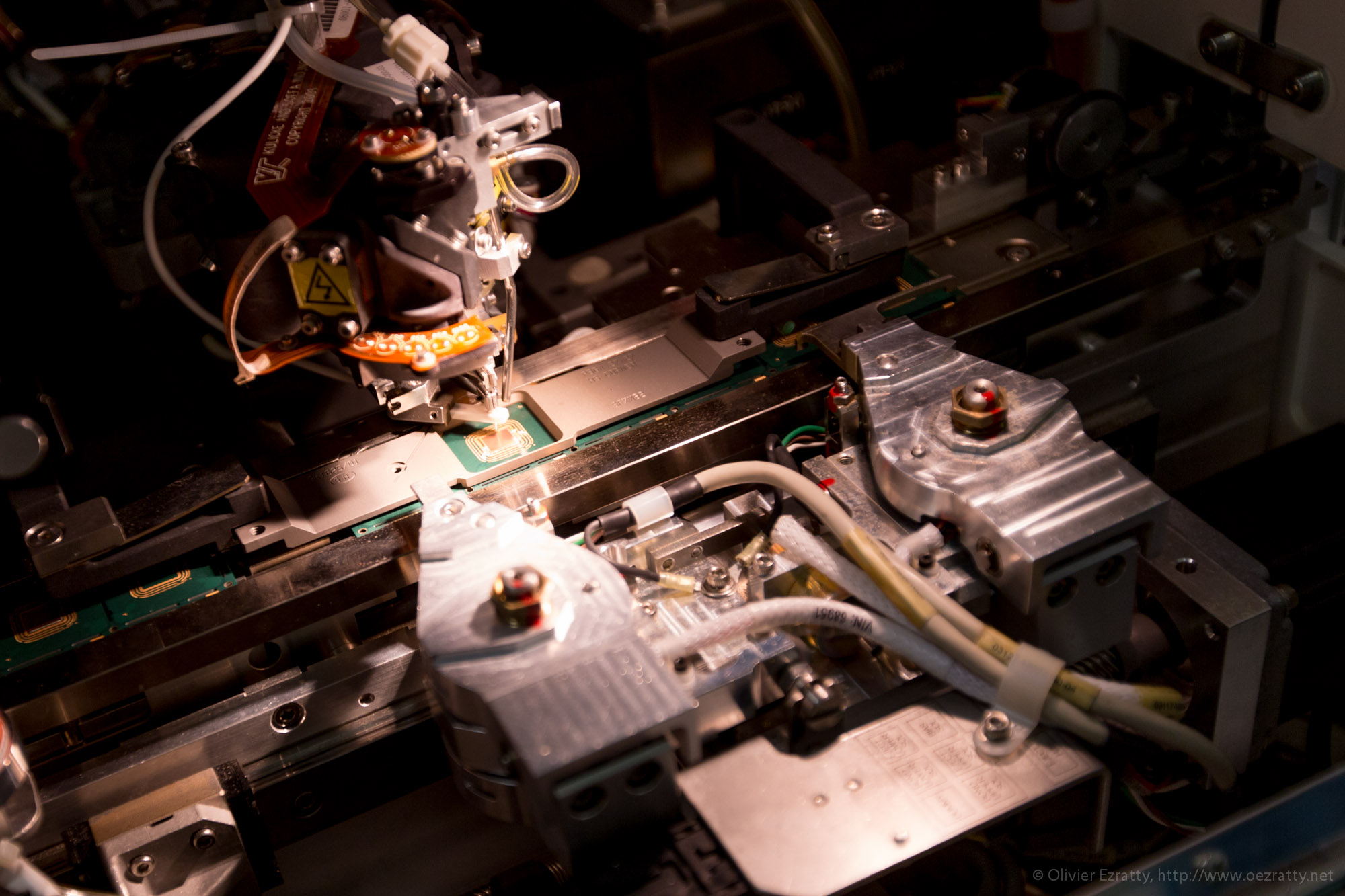

- Puis chaque puce est extraite du wafer pour être posée sur un substrat organique à plusieurs couches conductrices, l’adhésion étant faite à l’aide d’une colle qui sera ensuite cuite dans une étuve.

- Une machine va ensuite souder de minuscules fils de cuivre ou d’argent entre le substrat et la puce au niveau des contacts métalliques de celle-ci.

- Puis le boitier est moulé de façon à protéger la puce.

- Celui-ci est ensuite marqué au laser avec sa référence et son identifiant.

Il existe plusieurs sortes de packaging selon la destination du produit et notamment les PGA, BGA et PLCC. Cette unité de packaging peut tous les fabriquer en fonction des besoins.

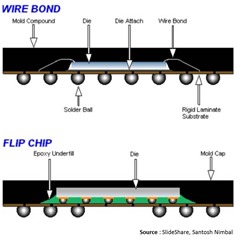

- PGA (Pin Grid Array), avec un support carré et des pins qui se connectent à un socket. C’est le format habituel des processeurs Intel pour PC desktop.

- BGA (Ball Grid Array), avec un support carré et une matrice de billes de soudure destinée à être directement soudées sur une carte mère. Il est utilisé dans les set-top-box et les mobiles. On distingue le BGA FC (Flip Chip) où la puce est connectée au substrat du package par des bumps et le BGA WB (Wire Bond) où la puce est connectée aux substrats du package via des fils en or, cuivre ou argent.

- PLCC (Plastic Leaded Chip Carrier), avec un boitier plastique et des pattes sur le côté qui est généralement monté en surface sur les circuits imprimés.

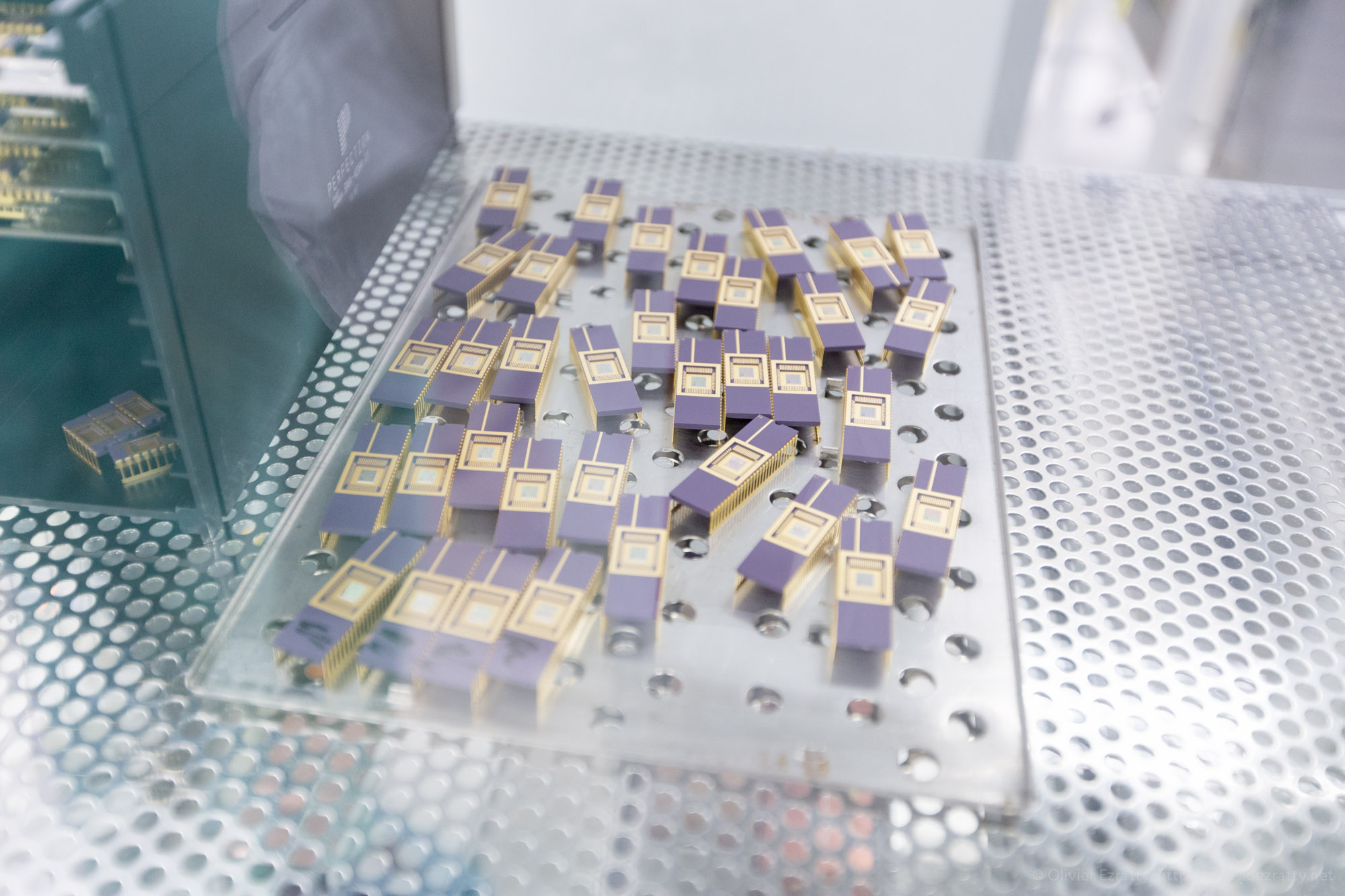

- Céramique : des packages utilisés pour les composants RF ou pour des tests, où la puce est posée sur un substrat en céramique isolante, avec des pins sur le côté qui s’insèrent dans les trous d’une carte mère.

- Packages spécifiques pour les puces optiques (cf cette présentation du CEA-LETI qui en explique les enjeux).

Grenoble – unité de tests

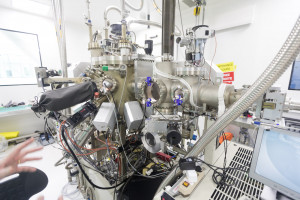

Derrière l’unité de packaging se situe une unité de tests qui à assurer le test des wafers qui viennent tout juste de sortir de la Fab et puis ensuite le test des chipsets une fois intégrés dans leur package.

Le premier test appelé EWS (Electrical Wafer Sorting) sert à éliminer les chipsets non conformes sur les wafers dès leur sortie de l’usine et avant leur mise en boîtier.

Il se trouve qu’environ 3% de la surface des chipsets est dédiée aux tests. Une unité de pilotage des tests intégrée dans les chipsets est reliée par une couche métal dédiée à l’ensemble des modules fonctionnels du chipset. Cela permet à cette unité de gérer des tests unitaires de chaque module.

Ce test des chipsets lorsqu’ils sont encore sur leur wafer donne des indications à la fab sur la qualité des wafers et l’éventuelle dérive de son procédé. En identifiant les puces puces défaillantes, on fait ensuite l’économie de leur mise en boitier.

Le test EWS va stresser chaque puce en l’alimentant entre 80 % et 120 % de sa tension nominale et vérifier que les signaux de sortie sont bien conformes pour des signaux d’entrés donnés.

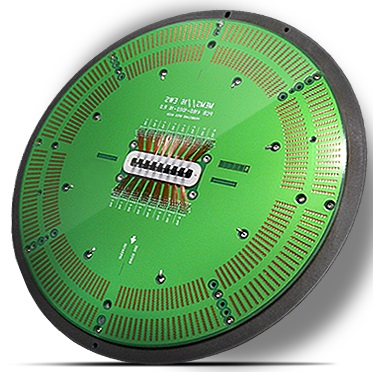

Les tests sont réalisés à l’aide d’une énorme machine de tests qui se connecte sur le circuit via une carte de tests (pour les pièces packagées) ou une carte à pointes (“probe cards” pour les wafers et l’EWS, exemple ci-dessous). La carte intègre des micro-contacteurs se connectant sur le circuit. Cette tête de 25 cm de diamètre peut couter jusqu’à 50K€ car elle est spécifique à chaque chipset testé.

Les “probe cards” de tests comprennent un circuit imprimé avec « des pointes » en tungstène-rhénium qui vont rentrer en contact avec la surface de la puce et assurer un contact électrique avec sa dernière couche de métallisation. Les pointes sont des tiges métalliques de 15 à 20 micromètres de diamètre à leur extrémité. Une carte de tests peut contenir jusqu’à plusieurs centaines de ces pointes. Voir cette vidéo qui explique le fonctionnement de cette étape de test de manière animée.

La babasse de gestion des tests comprend une batterie d’ordinateurs qui pilotent les tests en passant par le module de tests du circuit. Si le test était réalisé au niveau fonctionnel avec un système d’exploitation classique genre Android, il durerait de longues minutes ! Ici, il est réalisé en quelques secondes par puces sachant qu’il y en a des centaines sur un wafer, selon leur taille.

L’unité de tests que j’ai visitée utilise aussi des machines de tests dotées de colonnes optiques dédiées aux capteurs photos.

Conclusion

Quand on visite de telles fabs, on est évidemment frappé d’un point clé sur les équipements : ils sont très rarement français. Le matériel est essentiellement américain (Applied Materials), hollandais (ASML, AMSI) ou Japonais (Disco). Seules quelques rares machines de tests et de mesure sont françaises. C’est à l’image de l’industrie française qui n’a jamais été très bonne dans le secteur des machines-outils.

J’ai aussi fait un tour rapide dans une grande salle de réunion qui servait pour l’occasion de salle de tests d’intégration pour le test fonctionnel de chipset de set-top-box. Il s’agissait visiblement de préparer les démonstrations des derniers chipsets prévues pour le CES de Las Vegas début janvier.

A l’entrée de l’un des bâtiments du site de Grenoble se trouve un nouveau showroom pour la présentation au grand public et aux salariés des processus de fab ainsi que des produits finis qui utilisent des composants d’origine ST, et notamment pas mal d’objets connectés que l’on peut croiser dans les allées du CES sans pour autant savoir qu’ils intègrent un composant STMicroelectronics, comme c’est le cas de nombreux smartphones et de nombreuses tabelttes.

STMicroelecronics aura comme d’habitude son grand showroom à Las Vegas au Encore, pendant le CES. Ils y valorisent notamment une bonne dizaine de startups et spécialistes français des objets connectés ou de la télévision numérique. En les intégrant, on arrivera sans doutes à près de 150 sociétés françaises présentes au prochaine CES, à comparer aux 109 que j’avais décomptées en 2014 et aux moins de 60 en 2013.

Cette croissance provient essentiellement de celle des startups présentes dans le secteur des objets connectés. Et finalement, même si on n’en parle pas souvent, STMicroelectronics est sans conteste le plus grand industriel de ce secteur en France !

![]()

![]()

![]()

Reçevez par email les alertes de parution de nouveaux articles :

![]()

![]()

![]()

Articles

Articles

A la découverte de la “fab” chez STMicroelectronics. 3/3 http://t.co/WtGgv8tUXk via @olivez cc @ST_World @anaisiou #passionnant

“@jeanlucbeylat: “A la découverte de la “fab” chez STMicroelectronics : 3” de @olivez sur http://t.co/OZMS8bhlu2“

[@ST_World #STMicroelectronics] Découverte de la fab chez STMicroelectronics EP3 : http://t.co/rMOYuP1EIS par @olivez http://t.co/p0wmkJ1ein