One 2026 quantum prediction is that it will to be the year when useful logical qubit based quantum computers will appear (dealt with prudently by Riverlane and Innovation Origins). In a sense, it would mark an irreversible transition from NISQ to FTQC.

Here, vendors face a complexity challenge not only to deliver what’s in their roadmaps but also when communicating about it. There are many underlying concepts and figures of merit that deserve to be explained. All vendors logical qubit are not born equal and are also not necessarily yet useful. To be so, they should support larger (much) quantum circuits than current NISQ quantum computers who are currently limited to about a thousand operations, and 5 to 6 thousands when using quantum error mitigation techniques.

I am self-publishing here a paper designed to help you understand the field of quantum error correction, logical qubits, and fault-tolerance, from the scientific and technology standpoints. As I did in other cases, this is organized as a large FAQ, based on the typical questions you may ask yourself when looking at vendors logical qubits announcements. It shows the links between the concepts, techniques, figures of merit, software and hardware components. It is written for multiple audiences, and particularly for quantum circuit developers who want to understand how and when their large circuits will be supported by FTQC systems, and which associated figures of merit are relevant. I also consolidate the experimental and theoretical work from FTQC industry vendors.

You can download it here or with clicking on the image below (45 pages PDF).

This paper is structured as follows:

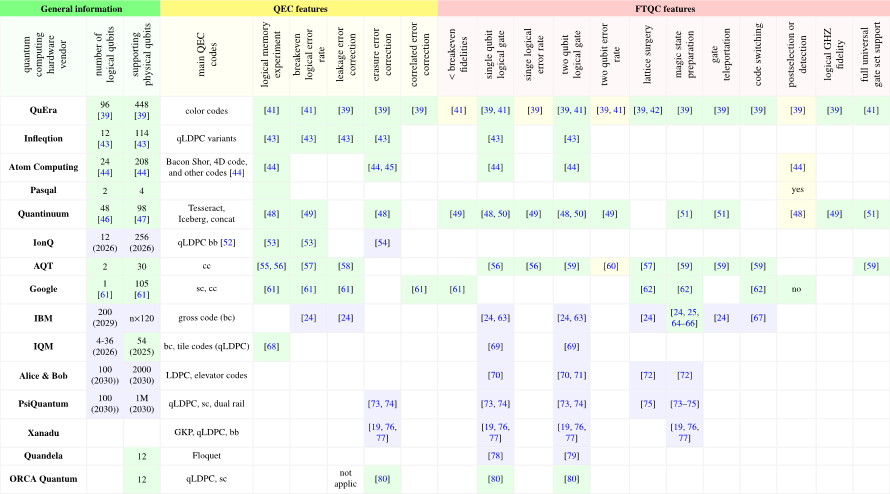

- Introduction which looks at what computer information science specialists may look for in industry vendor achievements as well as roadmaps, and how to find it. It describes the difference between quantum error correction and fault-tolerant quantum computing. It summarizes in a large table the key figures of merit of QEC and FTQC to look at when evaluating vendor’s achievements (below, look at the paper for the caption).

- QEC basics describes how quantum error correction works on a logical qubit memory, what types of errors are corrected and how. It is focused on surface, color, and qLDPC codes.

- Logical qubits describes some basics on the very notion of logical qubits and some related sizing aspects.

- Fault-tolerance describes the key features of fault-tolerance and how they are implemented, particularly for the realization of logical quantum gates. It quantifies the space, time and energetic overheads of QEC/FTQC.

- Industry vendors QEC-FTQC outlook describes the current achievements from industry vendors across multiple qubit modalities as well as maturity with a mix of experiments, theoretical work, and blueprints. This work often comes from the vendors and from the academic labs which are working with them.

The TL;DR summary is that vendors drive two heavy locomotives in parallel: develop error correction and fault-tolerance algorithmic solutions, and improving the scaling of their hardware as well as gate operations fidelities. The slower they are in the second, the harder it is for them to deliver fully functional logical qubits.

I wholeheartedly thank Jean-Philippe Nominé (CEA), Michael Vasmer (Inria), Anthony Leverrier (Inria), Valentin Savin (Quobly), Boris Bourdoncle (Quandela), Jérémie Messud (TotalEnergies), Thomas Monz (AQT), Andrés Gómez (CESGA), Marco Fellous-Asiani (Inria), Christophe Vuillot (Alice & Bob), François-Marie le Régent (Pasqal) and Nicolas Delfosse (IonQ), who provided me useful feedback and references to improve this paper. And Alan Ho, Jerry Chow and Jack Krupansky who also suggested changes in the paper after it was published and that are taken into account in the current version.

![]()

![]()

![]()

Reçevez par email les alertes de parution de nouveaux articles :

![]()

![]()

![]()

Articles

Articles