L’électronique supraconductrice

Post de Olivier Ezratty du 22 juin 2020 - Tags : Composants,Quantique,Technologie,USA | 1 Comment

J’ai eu le plaisir d’intervenir jeudi 18 juin 2020 dans une masterclass sur le “Hardware de l’IA” pour le Hub France IA qui durait deux heures (vidéo). J’y faisais un tour assez large et technique de la grande diversité des solutions matérielles d’accélération des applications de l’intelligence artificielle. J’y couvrais surtout la question des processeurs spécialisés et de la mémoire associée, en laissant un peu de côté le stockage et les télécommunications qui jouent aussi un rôle important.

Au détour de cette présentation, j’inventoriais différentes technologies permettant d’accélérer les calculs dont une qui est peu connue, celle du calcul à base de composants électroniques supraconducteurs. Je l’ai aussi étudiée dans le cadre de la préparation de la troisième édition de mon ebook open source Comprendre l’informatique quantique, qui m’occupe depuis le début du confinement covidesque et que je prévois de publier début septembre 2020. Cette prochaine édition sera très enrichie de nombreuses nouvelles parties avec un contenu scientifique et technologique encore plus dense. J’y aborde en particulier le cas des technologies de pointe qui sont soit concurrentes soit complémentaires du calcul quantique. Celle-ci en fait partie.

Voici donc en avant-première le contenu de cette nouvelle partie, parmi plein d’autres, de cette édition 2020. Je n’y intègre pas toutes les références et liens, que vous trouverez en bonne et due forme dans l’ebook en septembre 2020.

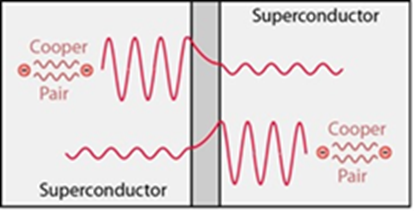

L’idée de créer des composants électroniques supraconducteurs capables de tirer parti de l’absence de résistance de composants à électroniques à basse température date du début des années 1960. Promue au départ par IBM, elle s’appuie en particulier sur la découverte de l’effet Josephson en 1962. L’effet Josephson décrit le passage de courant par effet tunnel dans un circuit supraconducteur et les effets de seuils associés. Le courant traverse une fine barrière isolante de quelques nanomètres d’épaisseur. En-dessous d’une certaine tension, le courant se met à osciller. Il est généré par les électrons organisés en paires de Cooper du nom de Leon Neil Cooper qui les a découverts en 1952. L’interprétation du phénomène de la supraconductivité n’a été formulée qu’en 1957 par John Bardeen (co-inventeur du transistor en 1947, deux fois prix Nobel de physique), Leon Neil Cooper et John Robert Schrieffer de l’Université de l’Illinois dans ce que l’on appelle la théorie BCS. En 1957, Cooper avait seulement 27 ans et il a obtenu le prix Nobel associé à 42 ans. Né en 1930, il est toujours de ce monde.

Ces électrons en paires de Cooper sont de spins opposés (polarité magnétique) et se constituent du fait du rapprochement des ions métalliques à leur passage. Le système se comporte comme une résistance associée à une inductance en boucle, l’oscillation étant contrôlable par un champ magnétique. Le physicien et prix Nobel de physique Serge Haroche explique l’effet Josephson dans cette vidéo de son cours du Collège de France de 2011.

Cet effet Josephson sert à faire fonctionner les qubits supraconducteurs d’ordinateurs quantiques comme ceux d’IBM, de Google, Rigetti, IQM (Finlande), Alice & Bob (France) et plein d’autres, y compris D-Wave avec ses calculateurs à recuit quantique qui s’appuie essentiellement sur l’effet tunnel. L’effet Josephson est aussi exploitable pour créer des transistors supraconducteurs qui ne vont pas faire appel aux mécanismes de la superposition et de l’intrication propres au calcul quantique. C’est de ça dont traite le reste de ce texte.

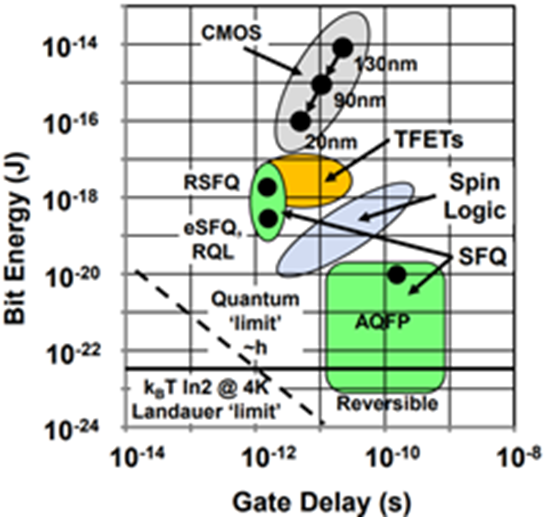

Leurs bénéfices attendus sont une baisse de la consommation d’énergie et une augmentation de la fréquence d’horloge des circuits. Donc, dessert et fromage !

Plusieurs générations de composants supraconducteurs se sont succédées depuis les années 1960 :

Il existe quelques autres variantes de composants supraconducteurs que je ne ferais que citer (SSV, SVJJ, STTJJ, S3JJ) car elles ne semblent pas courantes, sans compter la JMRAM pour la mémoire supraconductrice.

A ce jour, le record d’intégration de ce type de composant est de seulement 144 000 jonctions Josephson dans un chipset, réalisé en intégration 248 nm.

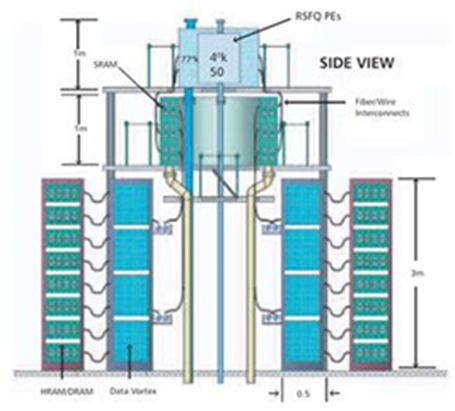

La NSA misait au milieu des années 2000 sur le RSFQ en y investissant $400m sur la période 2005-2010. Elle s’était donnée comme objectif de créer un processeur doté d’un million de portes logiques tournant à 50 GHz. Le document de la NSA décrivant le projet est étonnamment très détaillé et tout autant instructif. On y découvre l’étendue des défis technologiques à relever. Il y a notamment celui de la création de mémoires cryogéniques supraconductrices ou pas : hybride CMOS-jonction Josephson, SFQ ou monolithique RSFQ-MRAM. Puis la communication entre l’électronique cryogénisée et l’extérieur, a priori avec une bardée de fibres optiques à 25 Gbits/s que l’on ferait probablement monter aujourd’hui à 100 ou 200 Gbits/s.

Enfin, il faut dimensionner la cryogénie pour supporter un grand nombre de composants. Pour les tests, une simple tête pulsée et son compresseur suffisent. Des installations plus imposantes sont envisagées pour la montée en puissance, comme dans l’illustration ci-dessous. Mais la température requise est de 4K, bien moins contraignante que les 15 mK des qubits supraconducteurs. A 4K, un compresseur et une tête pulsée (qui viennent principalement de l’Américain CryoMech ou du Japonais Sumitomo) font l’affaire et consomment entre 5 et 12 kW. Le budget thermique à 4K qui peut être dépensé par l’électronique est d’au moins 1W ce qui permet de faire pas mal de choses. Quant aux supraconducteurs à température ambiante ou presque ambiante, ils existent en laboratoire mais nécessitent des pressions énormes incompatibles avec la production de composants électroniques en couches.

Le projet s’appuyait surtout sur la société Hypres, la seule société américaine entièrement dédiée à la création de composants supraconducteurs et dotée de sa propre fonderie depuis 1983. Ils fournissaient des composants radiofréquences à l’armée. Ils ont notamment développé un processeur 8 bits en RSFQ et 28 000 jonctions Josephson.

SeeQC (2017, USA, $11,8M) est une spin-off du groupe américain Hypres, spécialisée dans la création d’électronique supraconductrice et crée par John Levy, Matthew Hutchings et Oleg Mukhanov. Son nom signifie « Superconducting Energy Efficient Quantum Computing ». Elle se focalise dans la création de circuits de contrôle de qubits supraconducteurs eux-mêmes supraconducteurs dotés de mémoires à base de technologie spintronique (spin d’électrons).

Leur chipset de contrôle est conçu pour être placé à l’étage qui est la température de 4K du cryostat, le chipset quantique étant positionné dans un étage plus bas, à 15 mK. Il exploite des jonctions Josephson SFQ. Dénommé Digital Quantum Management (DQM) System-on-a-Chip, le circuit comprend les générateurs de micro-ondes de pilotage des qubits (avec DAC, des convertisseurs de signaux numériques en analogiques) et de l’électronique de lecture de l’état des qubits (avec des ADC, convertisseurs des signaux de micro-ondes analogiques en versions numériques). C’est censé énormément simplifier la connectique interne de l’ordinateur, enlevant une partie de ces câbles supraconducteurs ainsi que les composants d’atténuation et d’amplification de micro-ondes. La société a en fait été financée dans le cadre du projet C3 de l’agence IARPA lancé en 2016.

Il y a aussi Northrop Grumman avec sa fonderie située à Linthicum dans le Maryland. Enfin, étaient aussi impliquée l’Université Chalmers en Suède et divers laboratoires de recherche aux USA (JPL, Berkeley, Stony Brook) ainsi que le laboratoire de Boulder du NIST.

L’agence IARPA a pris le relai avec le projet Cryogenic Computing Complexity (C3) lancé en 2014. Il impliquait IBM, Northrop Grumman, Raytheon et Hypres et devait se terminer en 2018.

Ce projet s’intégrait à la National Strategic Computing Initiative (NSCI) lancée en 2015 par la Maison Blanche et qui portait sur le développement de supercalculateurs. Mais tout cela date de l’administration de Barack Obama et ne semble pas avoir été reconduit sous celle de Donald Trump. Il est difficile de trouver ce qu’a donné ce projet en 2020.

Hors USA, le Japanese Superconducting Computing Program ambitionnait en 2004 de créer un processeur tournant à 100 GHz générant 100 GLOPS en SFQ complété par 200 To de DRAM à 77K pour générer un système de 1,6 petaFLOPS comprenant 16384 processeurs. Le tout avec un cryostat consommant 12 MW et générant une puissance thermique de 18 kW à 4,2K. Il n’a pas encore vu le jour 15 ans plus tard. Ils arrivaient à créer le CORE1α en 2003 à 4999 JJ (jonctions Josephson) et tournant à 15 GHz, le CORE1β en 2006 à 10955 JJ tournant à 25 GHz, le CORE1γ avec 22302 JJ également à 25 GHz, le CORE100 en 2015 à 3073 JJ et 100 GHz, le COREe2 en 2017 à 10655 JJ et 50 GHz avec une mémoire intégrée. Voir Impact of Recent Advancement in Cryogenic Circuit Technology par Akira Fujimaki et Masamitsu Tanaka, 2017 (37 slides). En attendant, le supercalcutateur IBM Summit qui utilise des processeurs traditionnels et des GPUs génère 200 petaFLOPS en consommant 13 MW. Alors, pourquoi se décarcasser ?

La Chine a annoncé en 2018 un plan à $145m de construction d’un ordinateur supraconducteur pour 2022. Ils avaient alors créé une puce avec 10 000 jonctions Josephson. La Russie a aussi des ambitions dans le domaine.

En France, j’ai repéré que le laboratoire CMNE (Composants Micro Nano Electroniques) de l’IMEP-LaHC (Microélectronique, électromagnétisme, photonique, hyperfréquences) de l’UGA (Grenoble) travaillait dans ce domaine, sous la responsabilité de Pascal Febvre qui est basé sur le site de Chambéry. Citons aussi les amplificateurs cryogéniques à base de SQUIDs supraconducteurs à effet Josephson TWPA – travelling wave parametric amplifier – qui sont développés par l’Institut Néel (CNRS), le LPMMC (CNRS) et l’UGA à Grenoble avec notamment Nicolas Roch. Les composants de tests ont été fabriqués dans la Nanofab de l’Institut Néel de Grenoble. Voir A photonic crystal Josephson traveling wave parametric amplifier par Luca Planat & al, octobre 2019 (17 pages). On peut enfin citer un projet chinois allant dans le même sens, de générateur de micro-ondes supraconducteur pour le contrôle de qubits supraconducteurs s’appuyant sur un FPGA d’origine Xilinx.

Au final, cette filière des ordinateurs supraconducteurs est pour l’instant encore en suspens. Elle a souffert de l’avancée ininterrompue de la loi de Moore jusqu’à ces dernières années et aux difficultés de sa mise en œuvre pratique. Il n’est pas impossible que des synergies se développent entre le calcul quantique et cette branche un peu délaissée. Elles peuvent s’entre-aider comme on a pu le voir avec les circuits supraconducteurs de pilotage de qubits supraconducteurs ou silicium de SeeQC. Sait-on, le calcul quantique fera peut-être renaître indirectement cette filière !

Rendez-vous en septembre 2020 pour voir cette partie intégrée dans l’ebook “Comprendre l’informatique quantique” et d’autres technologies complémentaires ou alternatives au calcul quantique !

![]()

![]()

![]()

Lien du blog Opinions Libres : https://www.oezratty.net/wordpress

Lien de l'article : https://www.oezratty.net/wordpress/2020/electronique-supraconductrice/

Cliquez ici pour imprimer

(cc) Olivier Ezratty - http://www.oezratty.net